| 일 | 월 | 화 | 수 | 목 | 금 | 토 |

|---|---|---|---|---|---|---|

| 1 | 2 | 3 | 4 | 5 | ||

| 6 | 7 | 8 | 9 | 10 | 11 | 12 |

| 13 | 14 | 15 | 16 | 17 | 18 | 19 |

| 20 | 21 | 22 | 23 | 24 | 25 | 26 |

| 27 | 28 | 29 | 30 |

- 인공지능

- CNN

- Unsupervised learning

- 딥러닝

- SGD

- OpenGL

- logistic regression

- 그래픽스

- cs231n

- CPP

- Vision

- 백준

- recommender system

- Regularization

- C++

- 컴퓨터 비전

- 파이썬

- 신경망

- Kaggle

- SVM

- neural network

- pre-trained

- 추천 시스템

- Computer Vision

- 비용함수

- 머신러닝

- petal to metal

- 로지스틱 회귀

- Support Vector Machine

- 컴퓨터 그래픽스

- Today

- Total

kwan's note

9주차 - 메인 메모리(주 기억장치) 본문

수강일시 :12월 31일

출처: kmooc 컴퓨터구조

8주차는 중간고사로 수업이 없다.

9주차:기억장치 성능과 비용을 고려한 계층적 구조부터 반도체 메모리의 구조 및 설계에 관한 내용을 설명할 수 있다.

메모리의 경우는 궁금한점이 많았는데 수업에서 다루는 내용이 너무 당연하고 가벼워서 전체적으로 지루했다.

메모리는 adress x addressable unit의 구조를 띄고있다.

길이 x 폭으로 볼 수 있다.

16x8 bit를 예로 든다면

16개의주소가 있고 해당 주소에는

8bit짜리 data가 있는 것이다.

cpu가 access 하여 한번에 읽고 쓸 수 있는

비트의 수를 unit of transfer라고 하는데

종류에 따라 word, block이라고도 한다.

ssd의경우 block의 크기가 크다.

ACCESS TYPE

access type은 메인메모리와 보조저장장치가 다르다.

보조저장장치의 경우 순차탐색이나 direct access를 이용하는데 direct access도 블럭 내에서는 순차탐색을 한다.

탐색의 시간을 줄이기 위해 random access 또는 associate access를 할 수 있는데

메인메모리, 캐시는 이러한 방식을 사용하여 탐색의 시간을 줄인다.

메모리 계층구조

비싼건 빠르고 싼건 느리다.

이를 조합하여 적당한 가격에 affordable한 속도를 내도록 한다.

위쪽으로 갈수록 빠르지만 비싸다.

예를들어 메인메모리를 두어 이용확률이 높은 것들을 메인메모리에 올려 놓는다면 disk에 모든것을 저장하는것보다 훨씬 빠르게 이용할 수 있다.

RAM

Dram의경우 주기적으로 refresh해줘야 하고 속도가 SRAM에 비해 느리기 때문에 메인메모리에 사용하고 SRAM은 비용이 높아 캐시에 사용한다.

램 cs와 읽쓰 선택

D램의 구성

16M*4

dual inline pakage형태이다.

vcc +5V 양극 vss 0V 음극

data line 4개

address line은 16M= 2^24인데 A0~A11까지 address가 12개가있다.

CAS와 RAS로 row column활용해 조합을 할 수 있다.

column을 enable 하여 Column Address 버퍼를 통해서 데이터가 이동할 때는 Refresh Counter를 선택해서 Decoder를 통해서 기억소자에 있는 RC회로를 재충전하게 한다.

이를 조합하여 2^24개의 address를 만든다.

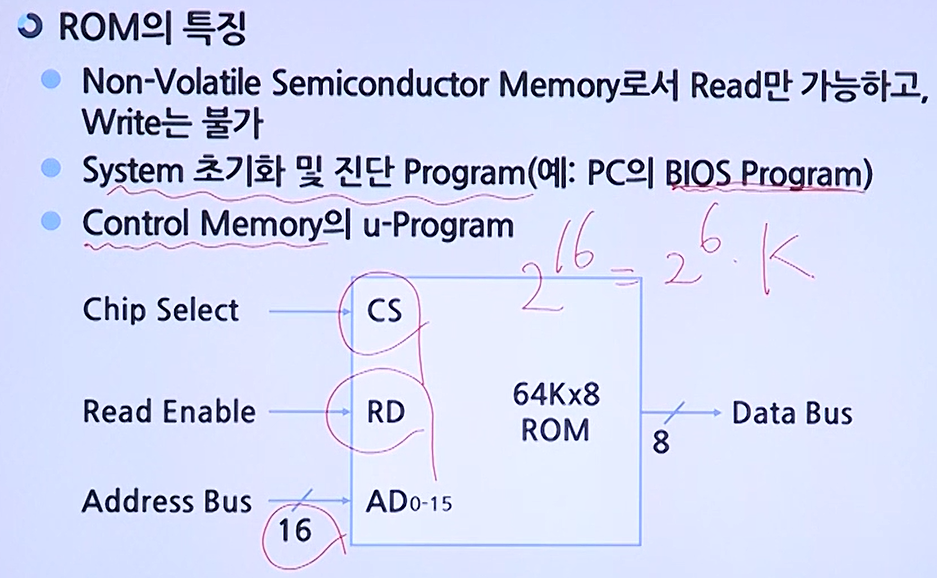

ROM

일반적으로 ROM은 지우기가 불가능하지만

EROM은 자외선으로 삭제가 가능하고 여러번 write할 수 있다.

EEPROM은 전기적으로 지울 수 있는 EPROM이고

flash memory는 block단위로 지울 수 있는 EEPROM이다.

메모리보다 필요한 data output이 긴경우

병렬연결하여 사용한다.

필요한 기억장치 용량이 기억장치 칩의 용량보다 큰 경우

칩들을 직렬연결하여 모듈을 구성한다.

'Computer Programming > Computer System' 카테고리의 다른 글

| 11주차 -보조저장장치 (ssd) (0) | 2020.12.31 |

|---|---|

| 10주차 - cache (캐시메모리) (0) | 2020.12.31 |

| 7주차-제어 유닛 (0) | 2020.12.30 |

| 6주차- 인터럽트(Interrupt)와 서브루틴(Subroutine), 파이프라이닝(Pipelining) (0) | 2020.12.29 |

| 5주차 - 명령어 사이클 (컴퓨터 처리) (0) | 2020.12.29 |