| 일 | 월 | 화 | 수 | 목 | 금 | 토 |

|---|---|---|---|---|---|---|

| 1 | 2 | 3 | 4 | 5 | ||

| 6 | 7 | 8 | 9 | 10 | 11 | 12 |

| 13 | 14 | 15 | 16 | 17 | 18 | 19 |

| 20 | 21 | 22 | 23 | 24 | 25 | 26 |

| 27 | 28 | 29 | 30 |

- Support Vector Machine

- 머신러닝

- 추천 시스템

- SGD

- Regularization

- 비용함수

- recommender system

- 로지스틱 회귀

- CNN

- Unsupervised learning

- 컴퓨터 그래픽스

- Vision

- 파이썬

- OpenGL

- neural network

- 신경망

- C++

- logistic regression

- 백준

- Kaggle

- 컴퓨터 비전

- 인공지능

- Computer Vision

- SVM

- cs231n

- 딥러닝

- CPP

- 그래픽스

- petal to metal

- pre-trained

- Today

- Total

kwan's note

1주차-컴퓨터 구조 개요 본문

수강일시 :12월 26일

출처: kmooc 컴퓨터구조

1주차: 컴퓨터를 구성하는 구성품을 설명하고 어떻게 연결할 것인가에 대해 알아본다.

메모리로부터 읽어온 데이터나 프로그램을 어떻게 처리하고 저장할 것인가에 대해 설명한다.

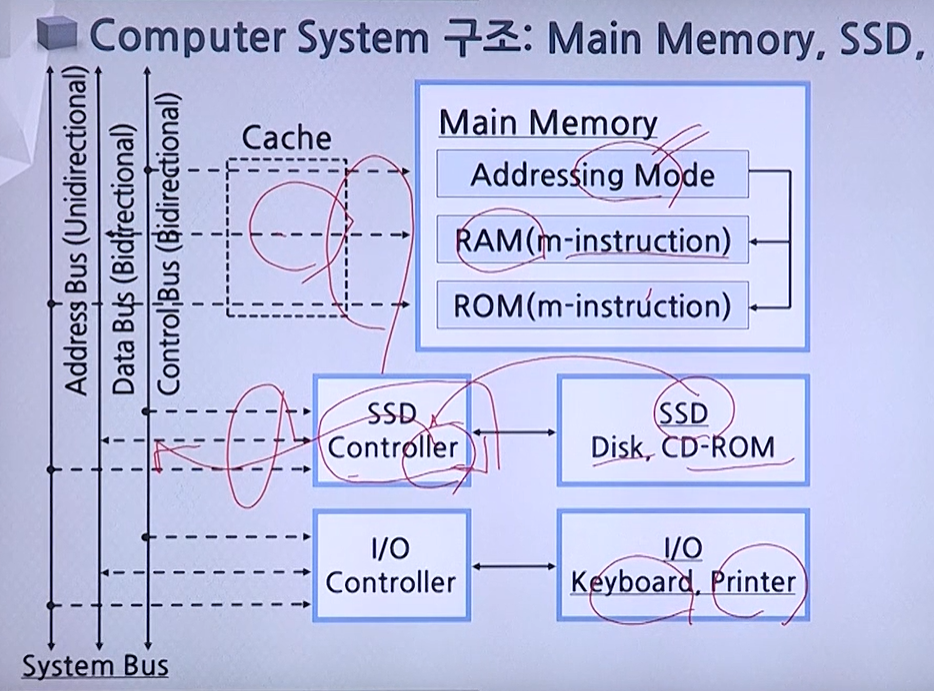

컴퓨터 시스템의 전반적인 구조는 CPU 메인메모리 보조저장장치, IO등으로 나뉘는데 각 구조는 bus로 연결이 되어있다.

CPU는 ALU, register set, control Unit으로 이루어져있는데

ALU는 직접적으로 논리연산을 수행하는 연산유닛이고 register set은 여러 레지스터들의 집합이다.

register set에는 shift register, status register의 일반목적 레지스터와 ACC SP PC MAR MBR IR등의 특수목적 레지스터로 나뉜다. ACC는 연산내용의 축적 SP는 상태포인터 PC는 수행할 주소를 저장하는 프로그램카운터, MAR은 메모리 주소 레지스터 MBR은 메모리 버퍼레지스터이고 IR은 instruction 즉 명령을 저장하는 레지스터다.

control unit은 instruction을 ID를 이용하여 해석하고 control 메모리에 주소를 지정하고 컨트롤버퍼 레지스터를 통해 control버스 레지스터로 이동해 출력된다.

메인 메모리에 접근할때 캐시를 두어 사용가능성이 높은 데이터는 캐시를 통해 빠르게 가져올 수 있도록한다. addressbus->cache->databus

만약 캐시에 없는데이터라면 메인메모리에서 데이터를 가져온다. 캐시에서 가져오는것보다는 속도가 느리다.

ssd와 입출력장치는 버스에 직접 연결되어있지 않고 컨트롤러를 통해 연결되있기때문에 더 느리다.

한번에 정해진만큼의 큰 데이터가 이동하게 된다.

데이터가 이동할때 control bus를 통해 상태변화를 주어 데이터가 전송되는지를 알린다.

즉 conrol bus에는 read/write등의 신호를 준다.

이를 받은 status register는 0 1등으로 변화하고 받는것을 완료하면 다시 이전상태로 돌아간다.

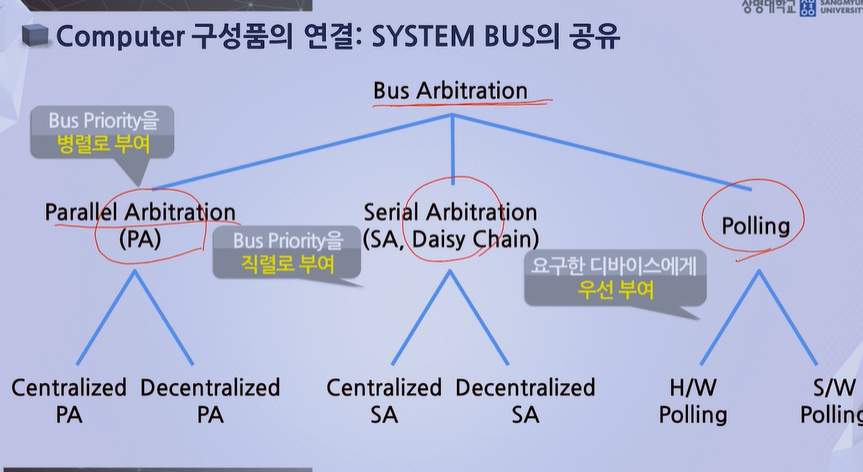

system 버스의 경우 우선순위를 부여하는 방법이 여러가지가 존재한다.

한번에 한종류만 이동이 가능하기 때문에 누구에서 bus우선권을 줄 것인가를 정해야 한다.

parallel 방식은 병렬로 serial의 경우 직렬로 polling의 경우 우선위(ex 시간순서)에 따라 bus를 할당한다.

IO device에 access하는 방식에도 여러가지가 있는데 다음과 같다

programmed I/O는 주기적으로 검색을한다. 정해진 시간마다 계속 검사하기 때문에 CPU의 자원을 많이 사용하게 된다. 따라서 만들기는 쉽지만 자원소모가 많기때문에 선호되지 않는다.

interrupt driven의경우 cpu에게 I/O가 입력되었음을 알린다. 즉 입력이 되면 입력상태변화를 통해 cpu가 변화를 인지하게된다. 가장 많이 쓰이는 방식이다.

마지막으로 DMA방식은 별도의 프로세서를 통해 data입출력을 관리한다.

1주차 수업은 대략적으로 컴퓨터 구조에 대해 소개하였다. 2주차부터 각 부분의 자세한 내용을 배울 것이다.

'Computer Programming > Computer System' 카테고리의 다른 글

| 5주차 - 명령어 사이클 (컴퓨터 처리) (0) | 2020.12.29 |

|---|---|

| 4주차-CPU의 구성 및 명령어 세트 (0) | 2020.12.29 |

| 3주차-arithmatic operation (0) | 2020.12.29 |

| 2주차-ALU -logic operations (0) | 2020.12.27 |

| 컴퓨터 구조 강의 (0) | 2020.12.26 |